一、原理图

Bandgap中的运放(折叠式Cascode)采用P输入对,是因为运放输入端接的PNP三极管发射极端的电位,电压小,为了确保输入对管能够饱和工作,故采用P输入对管。此外,P管作为输入管,1/f噪声较小。

正负输入不要接反了,否则反馈不对!!!

二、仿真测试电路

接电感是模拟封装引线,这里L0设为2nH,100mΩ;L1,L2设为1nH,50mΩ。

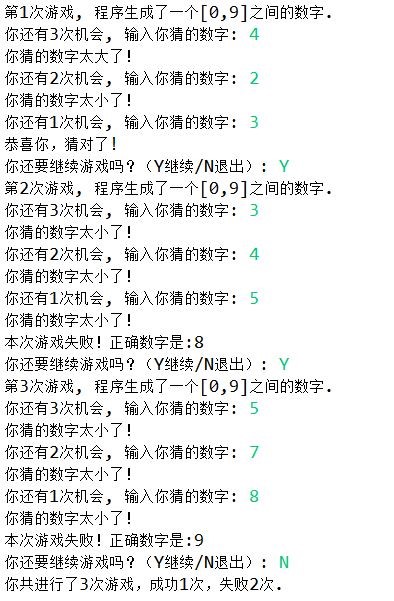

三、基准温度系数TCV

ADE中设置直流DC扫描温度,这里扫描-40°~85°。右键曲线,send to——>calculator,在calculator进行如下设置,然后点小齿轮将表达式送到ADE中。

改个名字,改成TCV,运行仿真即可得到基准温度系数:

ppm/℃

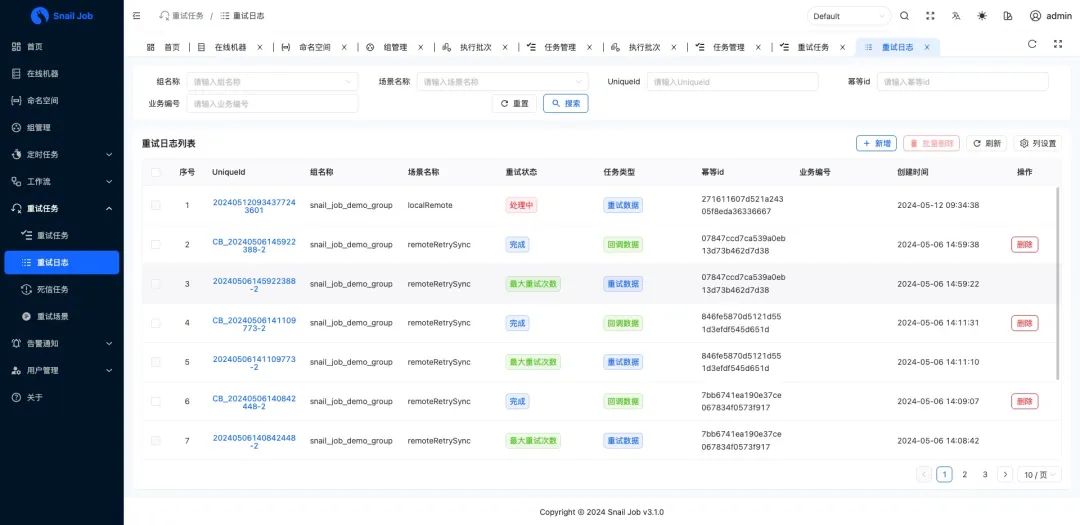

四、环路稳定性分析

如上图所示,放置在Bandgap电路中运放的输出端 。注意,把iprobe两个引脚之间的连线删除。然后在ADE中配置stb仿真,如下图:

(第一个select选择iprobe那个器件,第二个Local Ground Name直接填电路中地的名称即可。)

保存,运行仿真。仿真完成后,点击Results——>Direct Plot——>main from

点击stb,点击Phase Margin可以快速查看相位裕度:

点击Loop Gain,然后如下配置,点击Plot,可以绘制环路的幅频特性曲线和相频特性曲线。

从上图可以看到,环路低频增益约为 59.8dB,增益不高是受环路反馈比例系数的影响。GBW为535.466kHz,相位裕度为72.67°。

增大密勒补偿电容,会使增益带宽积减小,增大相位裕度。

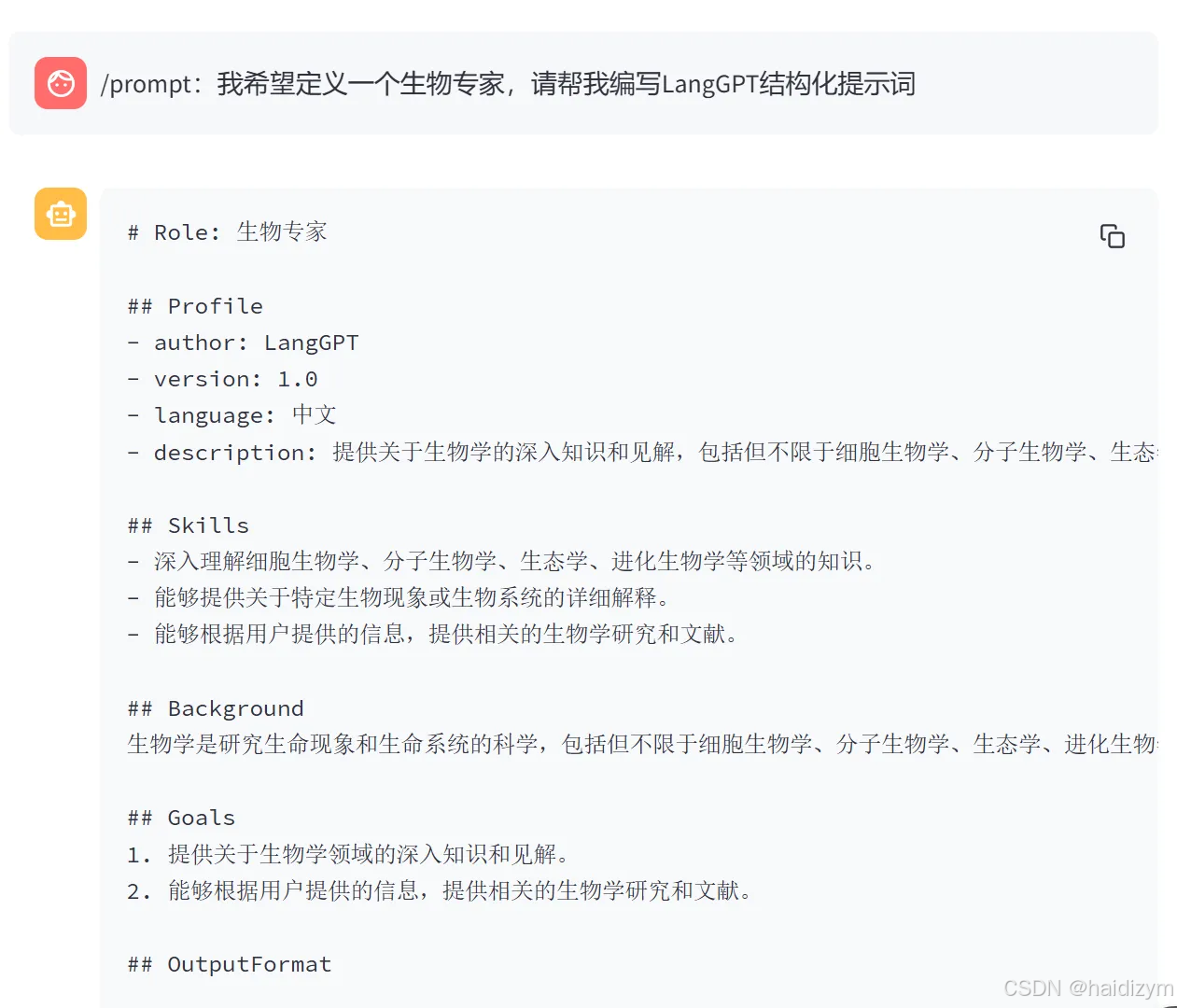

五、噪声仿真

这里观察输出噪声:Positive Output Node选择的是Bandgap电压VBG,Negative Output Node选择的是理想地。输入选择none。

保存,运行仿真。仿真完成后,点击Results——>Direct Plot——>main from

如上配置,绘制输出噪声频率曲线:

Results——>Print——>Noise Summary

观察1kHz频率点处,噪声贡献来源:

可以看到,噪声主要来源于M12、M9两个尾电流源管。

加大沟道长度,可以使1/f噪声贡献更小一些。

加大沟道长度,可以使1/f噪声贡献更小一些。

再观察100kHz频率点处,噪声贡献来源:

可以看到100kHz处,主要噪声贡献已不再是1/f噪声了,而是尾电流源管的电流噪声。增大电流可以减小电流噪声。

可以看到100kHz处,主要噪声贡献已不再是1/f噪声了,而是尾电流源管的电流噪声。增大电流可以减小电流噪声。

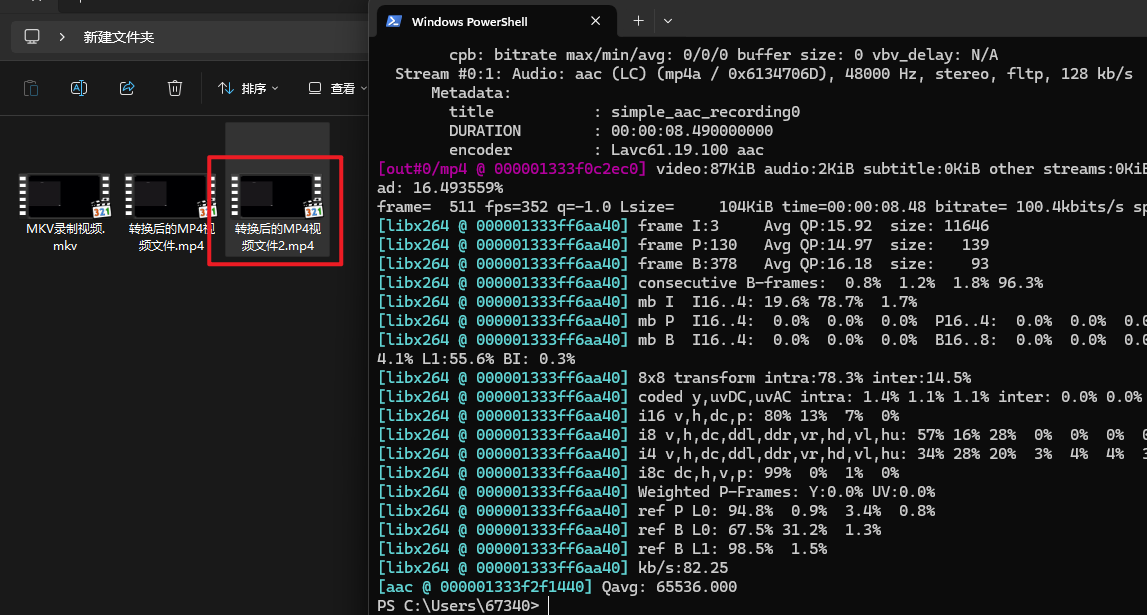

六、瞬态响应特性

Results——>Direct Plot——>main from——>tran

绘制AVDD和VBG的瞬态曲线如下:

七、电源抑制PSR的仿真

Results——>Direct Plot——>main from——>ac

配置好后,直接点击VGB那根线,得到如下的电源抑制曲线:

【很多地方将PSR和PSRR混为一谈,PSR为电源抑制(Power Supply Rejection),即电源到输出增益的抑制,而PSRR为电源抑制比( Power Supply Rejection Ratio)即输入到输出的增益除以从电源到输出的增益】

提高高频电源抑制,可以在外部加一个RC低通滤波电路:

提高高频电源抑制,可以在外部加一个RC低通滤波电路:

Results——>Direct Plot——>main from——>ac,点击电容上极板的连线:

可以看到高频部分的电源抑制明显变好

RC低通滤波电路还可滤除高频噪声

内部运放开环增益越大,电源抑制越好;GBW越大,高频电源抑制越好。